VHDL simulation with open source tools

In this tutorial I will show you how to simulate your VHDL designs with TerosHDL and GHDL.

GHDL is an open-source compiler and simulator for the VHDL hardware description language. It allows designers to simulate and test digital circuit designs written in VHDL, which is commonly used in the development of electronic systems.

GHDL is a command-line tool that supports VHDL-87, VHDL-93, VHDL-2002, and VHDL-2008 standards. It is designed to be highly portable and can run on a variety of platforms, including Windows, Linux, and macOS.

One of the key benefits of GHDL is that it can be used for both compilation and simulation. It can compile VHDL code into executable files that can be run on a simulator or FPGA, and it can also simulate the behavior of a digital circuit design, allowing designers to verify their designs before they are implemented in hardware.

Requirements

Follow all the steps to install TerosHDL and the requirements

GHDL installation

- Windows

- Linux

- Mac

- Install MinGW by downloading and running the MinGW installer from the MinGW website (http://www.mingw.org/). Follow the prompts to install MinGW to a directory on your computer, such as

C:MinGW. - Open the terminal or command prompt and type:

pacman -S mingw-w64-x86_64-ghdl

Open a terminal window by pressing Ctrl + Alt + T or searching for "Terminal" in the applications menu.. Type: sudo apt install ghdl

- Open a terminal window by going to Applications > Utilities > Terminal.

- Install Xcode, which includes Make, by running the following command:

xcode-select. This will prompt you to install the Xcode Command Line Tools, which includes Make. - Install Homebrew by running the following command in a Terminal window:

/bin/bash -c "$(curl -fsSL https://raw.githubusercontent.com/Homebrew/install/master/install.sh)". - Install GHDL by running the following command in a Terminal window:

brew install ghdl

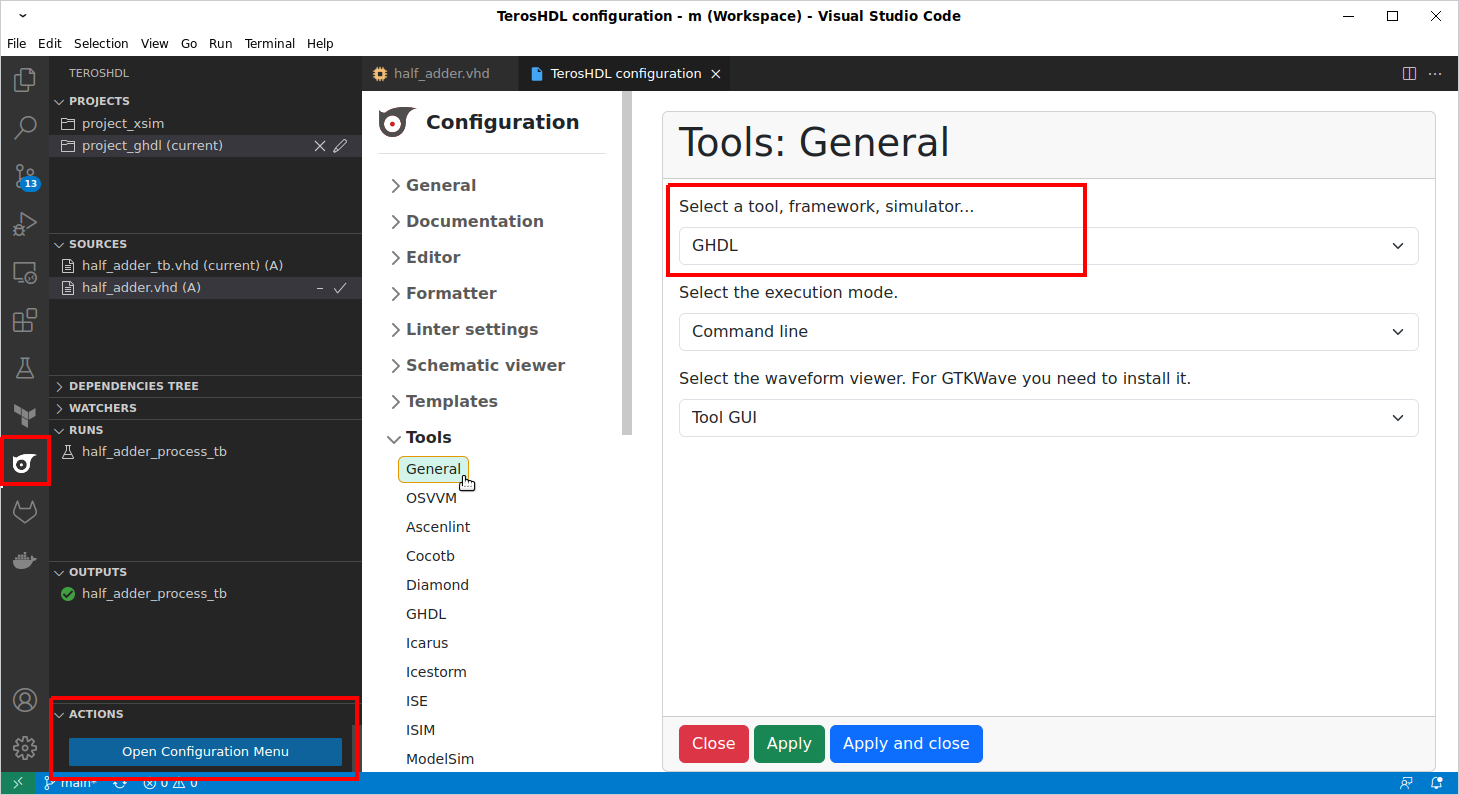

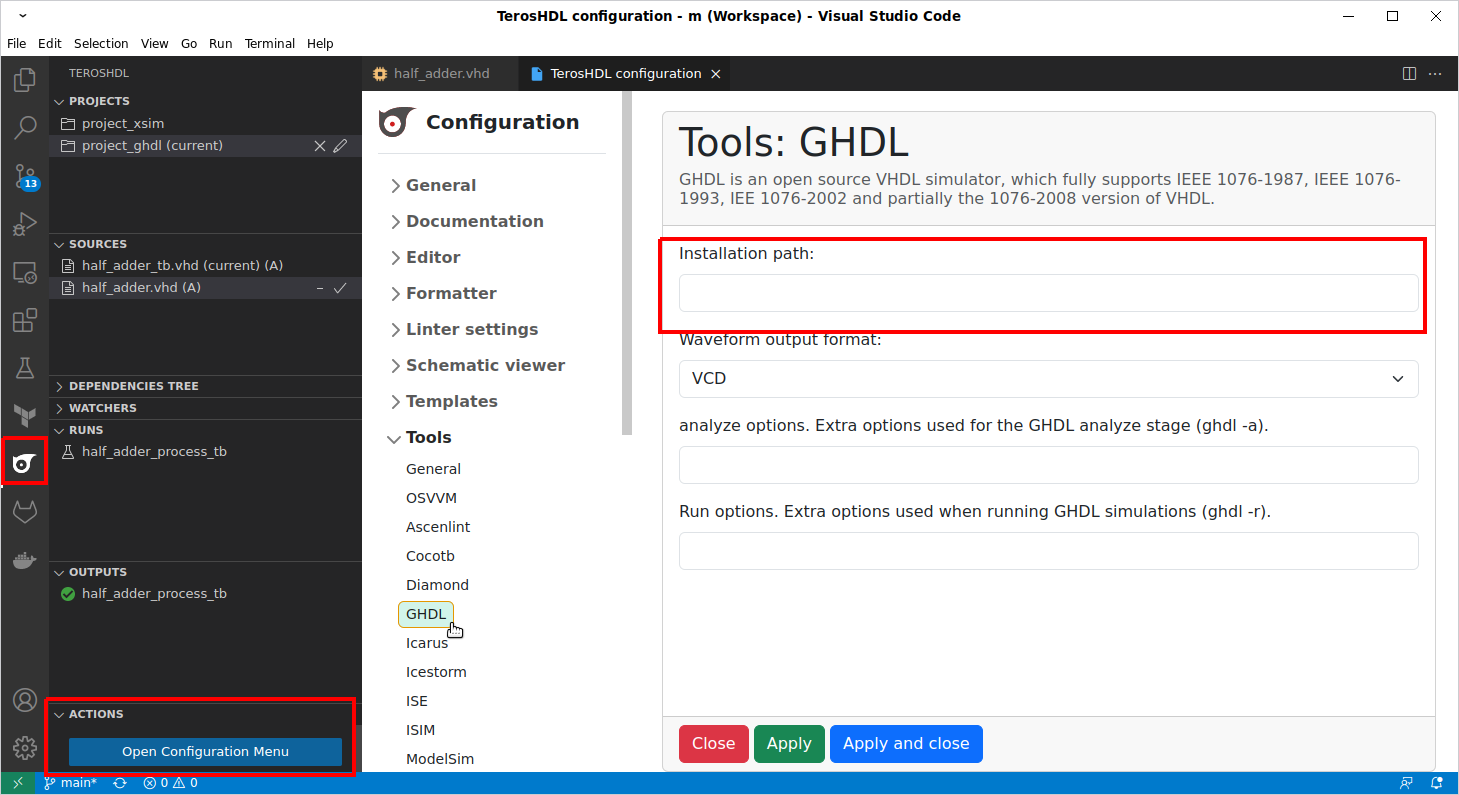

TerosHDL configuration

Select GHDL as tool:

Configure your GHDL installation path:

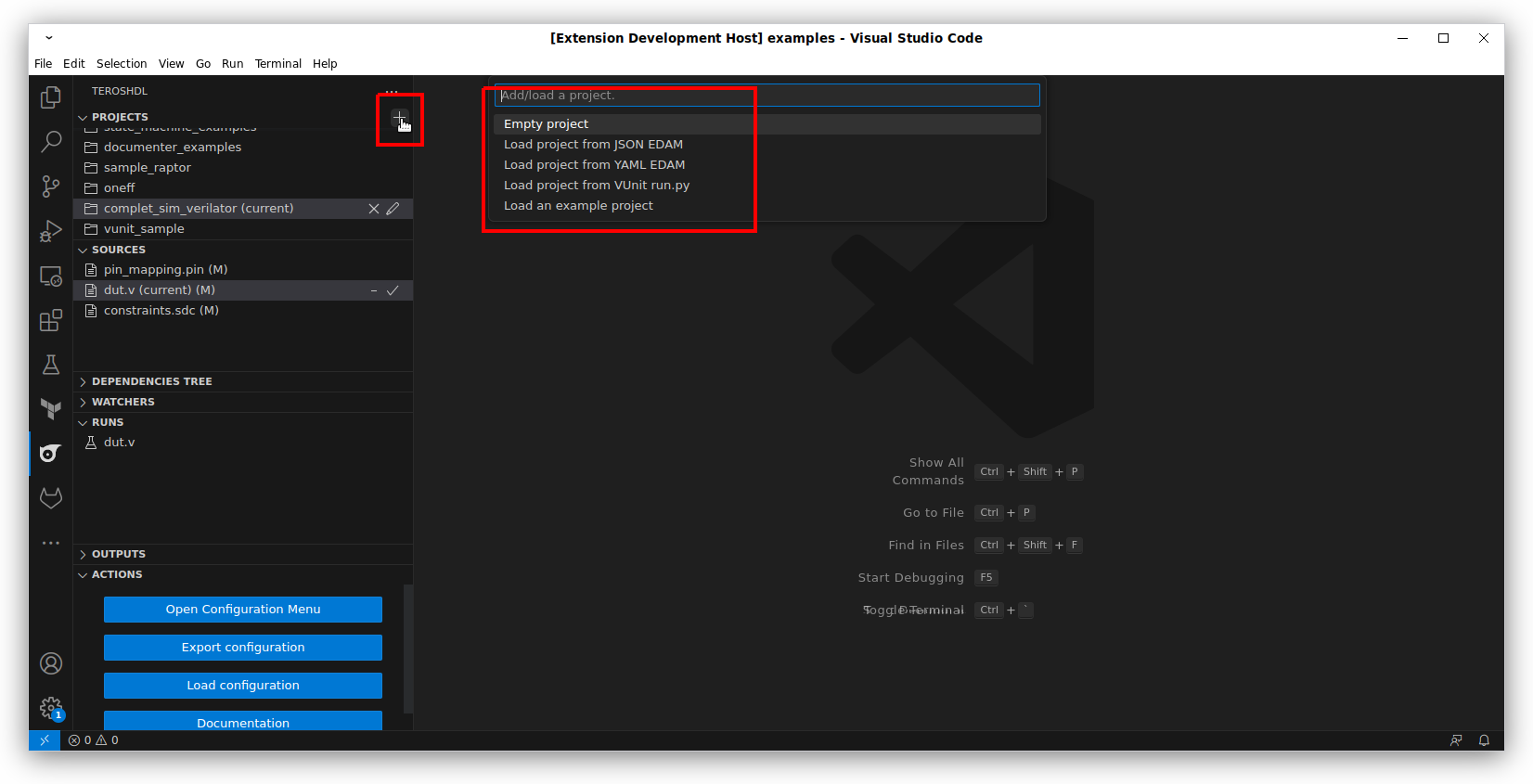

Adding an example project

Select: Load an example project -> GHDL

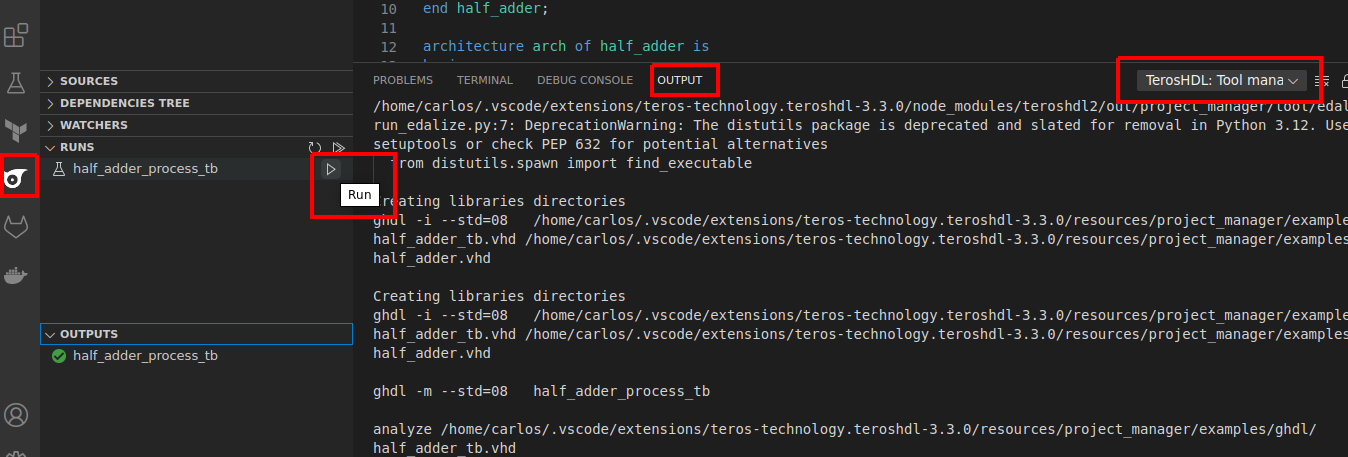

Running simulation

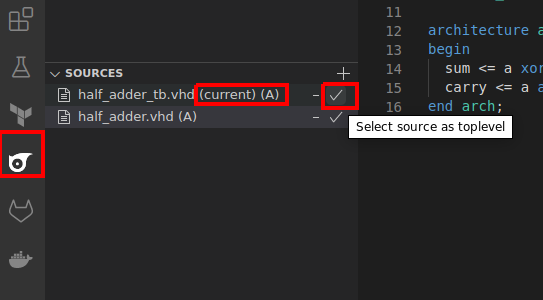

In sources view select half_adder_tb.vhd as top level. You will see (current) message in the file.

Run the test and check the output: