Templates

TerosHDL includes a powerful feature for the intelligent generation of templates, allowing users to quickly create testbenches and entity skeletons. The system automatically adapts to the specific context and design, offering a customized template that reduces manual work and increases productivity. Here is a table with the list of templates according to the language:

| Template | SV/Verilog | VHDL | Description |

|---|---|---|---|

| Testbench | Yes | Yes | HDL testbench |

| VUnit Testbench | Yes | Yes | HDL VUnit testbench |

| cocotb | Yes | Yes | cocotb python example |

| Signals | Yes | Yes | Port as signals |

| Component | Yes | Yes | Entity as component declaration |

| Instance | Yes | Yes | Entity as instance declaration |

| Instance | Yes | Yes | |

| Cross language instance | Yes | Yes | |

| Cross language testbench | Yes | Yes | |

| Cross language VUnit testbench | Yes | Yes | |

| Verilator | Yes | No | Verilator C++ example |

Step by step

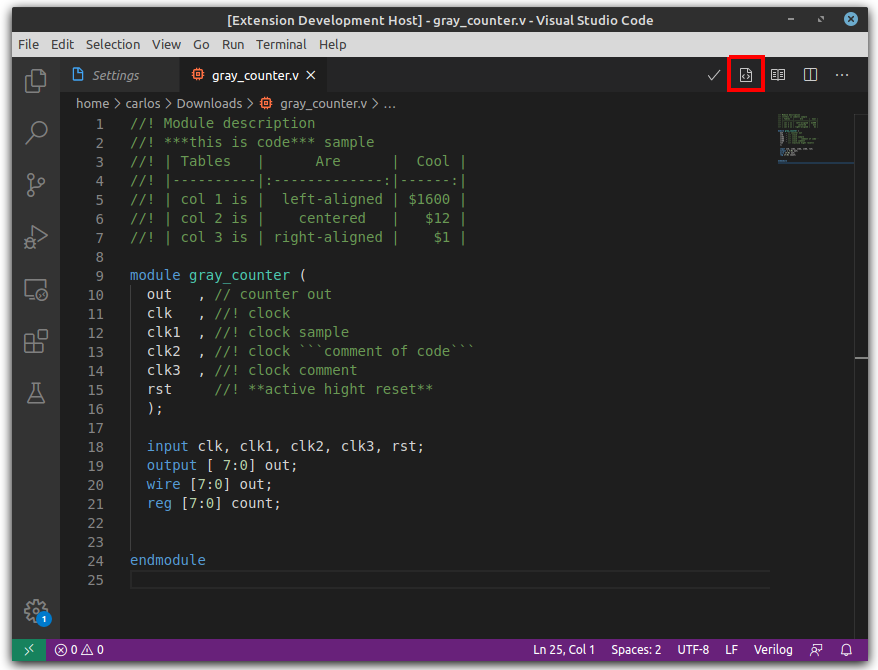

- Open a Verilog/SV/VHDL file and push the template generation button.

Image 1: Step 0

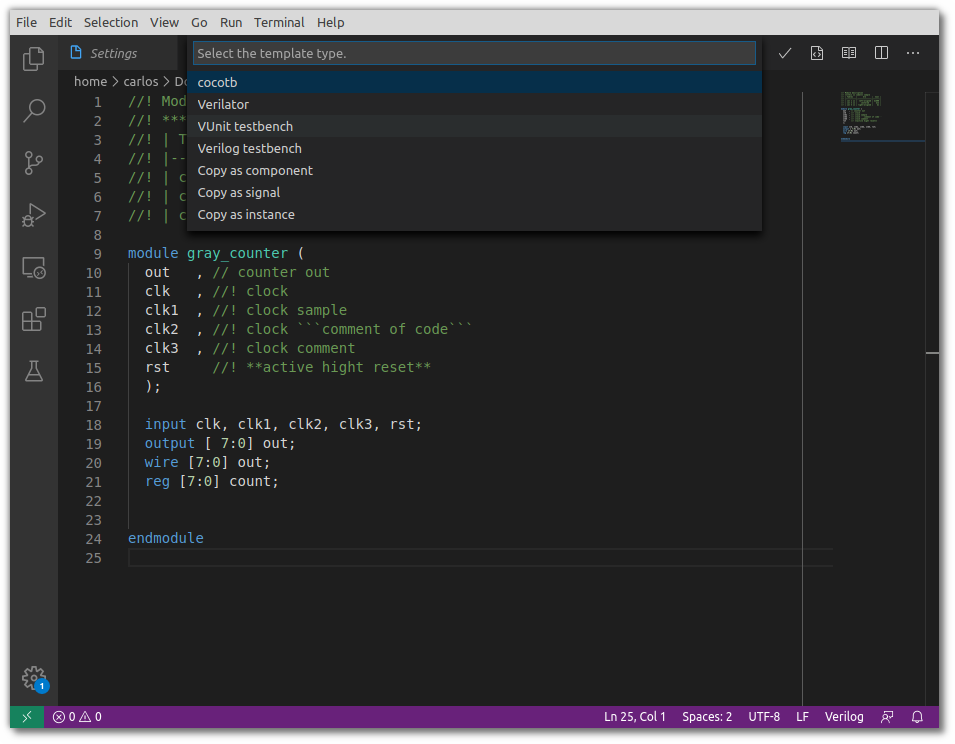

- Select the desired template from the list.

Image 1: Step 1

- The template will be stored in the clipboard and ready to be pasted Ctrl+v anywhere.

caution

Make sure that the cursor is in the editor view. So TerosHDL can detect the active document