Virtual Bus

Virtual bus allows you to create additional documentation sections of groups of signals which are related.

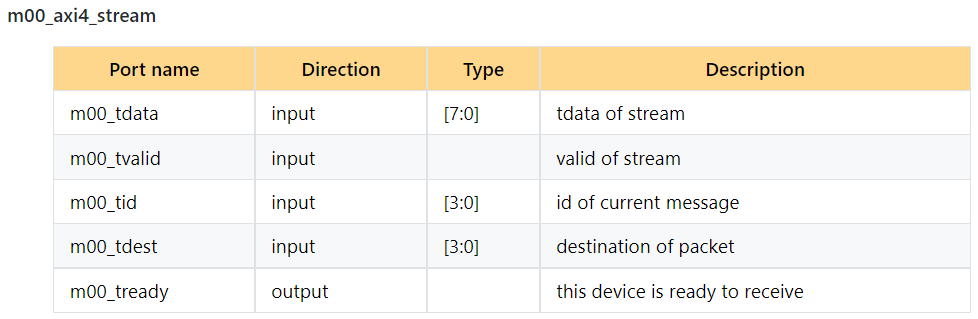

Each virtual bus you'll define will create a new table like this:

Image 1: Virtual bus Example

Which was generated by the following verilog code:

module virtualbus (

//! @virtualbus m00_axi4_stream @dir in

//! tdata of stream

input [7:0] m00_tdata,

//! valid of stream

input m00_tvalid,

//! id of current message

input [3:0] m00_tid,

//! destination of packet

input [3:0] m00_tdest,

//! this device is ready to receive

output reg m00_tready,

//! @end

input clk,

input rstn

);

endmodule

by default, the documenter will use --! (in VHDL) and //! (in Verilog) to recognize things to document.

Virtual Bus Syntax

The syntax for the virtual bus is as follows

-

To start a virtual bus, begin the group with

//! @virtualbus BUSNAMEand close the group with//! @end -

after the BUSNAME, you can add a description for the virtual bus.

-

To choose the direction of the virtual bus, add

@dir inor@dir outrespectively -

If you don't want the signals to be grouped in the block diagram, you can add

@keepports -

you can add description to each port in the virtual bus either Above or Inline with the port.